DS07-12506-4E

# 8-bit Proprietary Microcontroller

**CMOS**

# F2MC-8L MB89150/150A Series

# MB89151/151A/152/152A/153/153A/154/154A/155/155A MB89P155/PV150

#### **■** DESCRIPTION

The MB89150/A series has been developed as general-purpose version of the F<sup>2</sup>MC\*-8L family consisting of proprietary 8-bit, single-chip microcontrollers.

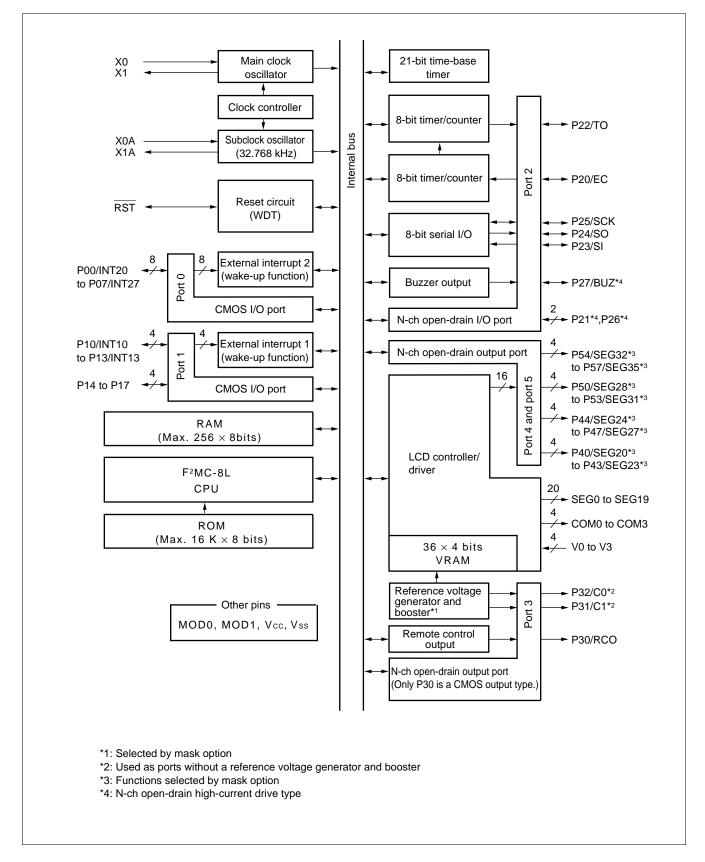

In addition to a compact instruction set, the MB89150 series microcontrollers contain a variety of peripheral functions such as dual-clock control system, five operating speed control stages, timers, a serial interface, a remote control transmission output, external interrupts, an LCD controller/driver, an LCD booster, and a watch prescaler.

\*: F<sup>2</sup>MC stands for FUJITSU Flexible Microcontroller.

#### **■ FEATURES**

- F<sup>2</sup>MC-8L family CPU core

- Dual-clock system

- · High-speed processing at low voltage

- Minimum execution time: 0.95 μs/2.7 V, 1.33 μs/2.2 V

- I/O ports: max. 43 channels

- 21-bit time-base timer

- 8/16-bit timer/counter: 1 channel (8 bits × 2 channels)

- 8-bit serial I/O: 1 channel

- LCD controller/driver: Max. 36 segments × 4 commons (built-in booster)

- · Remote control transmission output

(Continued)

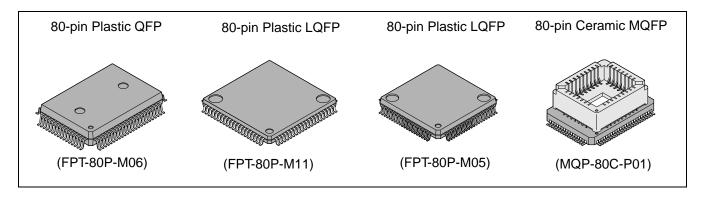

### **■ PACKAGE**

## (Continued)

- Buzzer output

- Watch prescaler (15 bits)

- External interrupts (wake-up function)

Four independent channels with edge detection function plus eight level-interrupt channels

## **■ PRODUCT LINEUP**

| Part number Parameter                  | MB89151/A                                                              | MB89152/A                                                                                                                                                                                                                                                                                                                                                                                     | MB89153/A                              | MB89154/A                             | MB89155/A                             | MB89P155                                                                                             | MB89PV150                          |

|----------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------|

| Classification                         |                                                                        | Mass production products (mask ROM products)  One-time PROM product                                                                                                                                                                                                                                                                                                                           |                                        |                                       |                                       |                                                                                                      |                                    |

| ROM size                               | 4 K × 8 bits<br>(internal<br>mask ROM)                                 | 6 K × 8 bits<br>(internal<br>mask ROM)                                                                                                                                                                                                                                                                                                                                                        | 8 K × 8 bits<br>(internal<br>mask ROM) | 12 K×8 bits<br>(internal<br>mask ROM) | 16 K×8 bits<br>(internal<br>mask ROM) | 16 K×8 bits<br>(internal<br>PROM,<br>programming<br>with general-<br>purpose<br>EPROM<br>programmer) | 32 K × 8 bits<br>(external<br>ROM) |

| RAM size                               | 128 × 8 bits                                                           |                                                                                                                                                                                                                                                                                                                                                                                               | 1                                      | 256 × 8 bits                          | 1                                     |                                                                                                      | 512 × 8 bits                       |

| CPU functions                          | Instruc<br>Instruc<br>Data b<br>Minimu<br>Interru                      | Number of instructions: 136 Instruction bit length: 8 bits Instruction length: 1 to 3 bytes Data bit length: 1, 8, 16 bits Minimum execution time: 0.95 μs/4.2 MHz Interrupt processing time: 8.57 μs/4.2 MHz                                                                                                                                                                                 |                                        |                                       |                                       |                                                                                                      |                                    |

| Ports                                  | Output<br>I/O poi                                                      | I/O port (N-ch open-drain):  8 (6 ports also serve as peripherals, 3 ports are a high-current drive type.)  Output port (N-ch open-drain):  18 (16 ports also serve as segment pins, 2 ports serve as boost capacitor connection pins.)*1  I/O port (CMOS):  16 (12 ports also serve as an external interrupt.)  Output port (CMOS):  1 (Also serves as a remote control.)  Total:  43 (max.) |                                        |                                       |                                       |                                                                                                      |                                    |

| Timer/counter                          |                                                                        | 8-bit timer co                                                                                                                                                                                                                                                                                                                                                                                | ounter × 2 cha                         | nnel or 16-bit                        | event counte                          | r × 1 channel                                                                                        |                                    |

| 8-bit serial I/O                       |                                                                        |                                                                                                                                                                                                                                                                                                                                                                                               | LSB firs                               | 8 bits<br>t/MSB first sel             | ectability                            |                                                                                                      |                                    |

| LCD controller/<br>driver              | Segment output: 32 (max.)*1 voltage Bias power supply pins: 4 generate |                                                                                                                                                                                                                                                                                                                                                                                               |                                        |                                       | generator<br>and booster<br>for LCD   |                                                                                                      |                                    |

| External interrupts (wake-up function) | 4 (edge selectability)<br>8 (level interrupt only)                     |                                                                                                                                                                                                                                                                                                                                                                                               |                                        |                                       |                                       |                                                                                                      |                                    |

| Buzzer output                          |                                                                        | 1 (7                                                                                                                                                                                                                                                                                                                                                                                          | ' frequencies                          | are selectable                        | by the softwa                         | are.)                                                                                                | _                                  |

## (Continued)

| Part number Parameter              | MB89151/A                                                                | MB89152/A                                          | MB89153/A | MB89154/A | MB89155/A | MB89P155 | MB89PV150                            |

|------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------|-----------|-----------|-----------|----------|--------------------------------------|

| Remote control transmission output |                                                                          | 1 (Pulse width and cycle are software selectable.) |           |           |           |          |                                      |

| Standby modes                      |                                                                          | Sleep mode, stop mode, and watch mode              |           |           |           |          |                                      |

| Process                            |                                                                          | CMOS                                               |           |           |           |          |                                      |

| Operating voltage*2                | 2.2 V to 6.0 V (single clock)/2.2 V to 4.0 V (dual clock) 2.7 V to 6.0 V |                                                    |           |           |           | o 6.0 V  |                                      |

| EPROM for use                      |                                                                          | MBN -201                                           |           |           |           |          | MBM27C256A<br>-20TV (LCC<br>package) |

<sup>\*1:</sup> Selected by the mask option. See section "■ Mask Options."

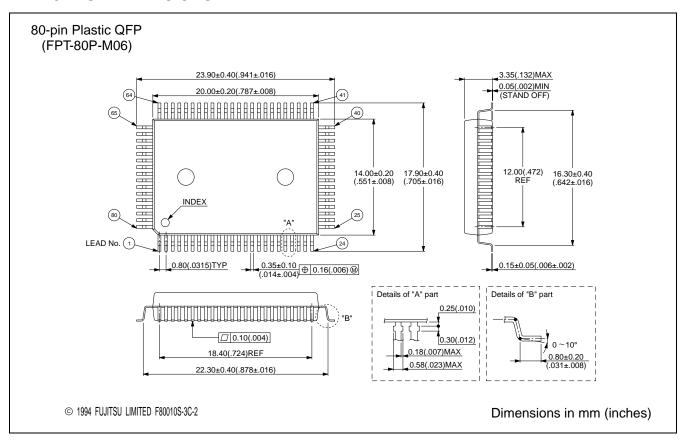

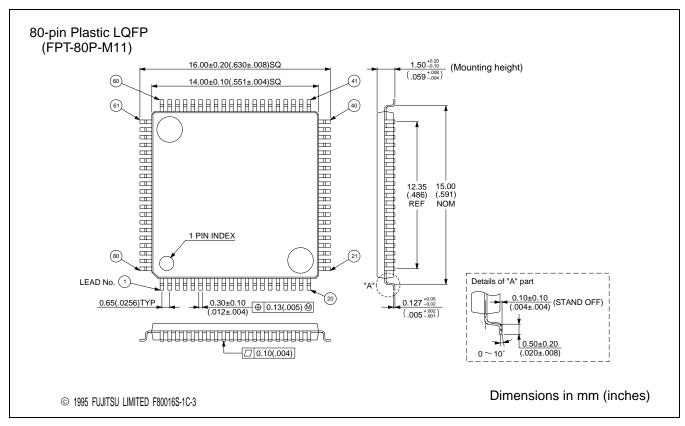

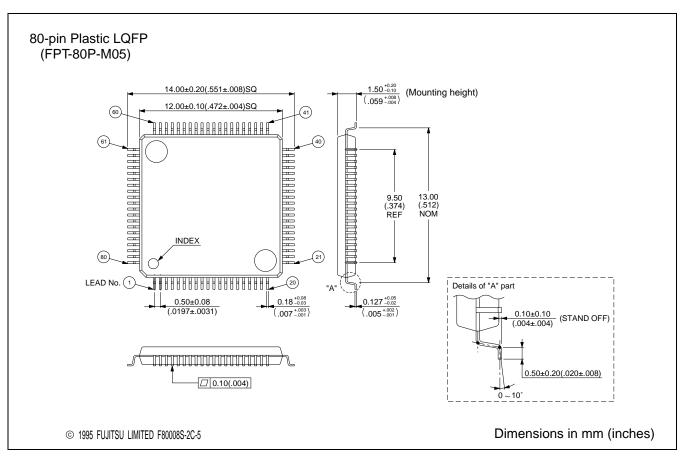

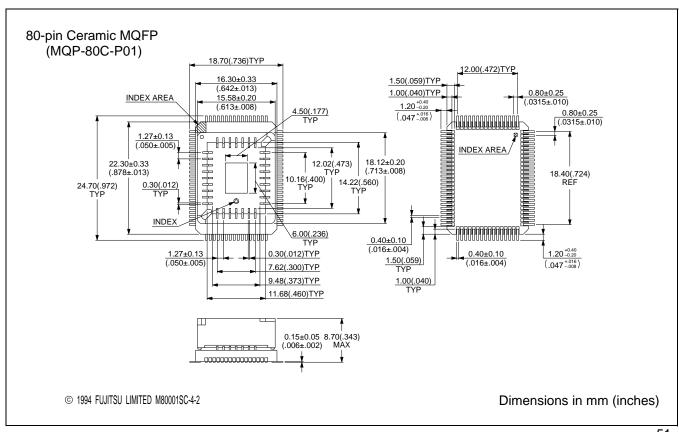

### ■ PACKAGE AND CORRESPONDING PRODUCTS

| Package     | MB89151/A<br>MB89152/A<br>MB89153/A<br>MB89154/A<br>MB89155/A | MB89P155 | MB89PV150 |  |

|-------------|---------------------------------------------------------------|----------|-----------|--|

| FPT-80P-M06 | 0                                                             | 0        | ×         |  |

| FPT-80P-M11 | 0                                                             | 0        | ×         |  |

| FPT-80P-M05 | 0                                                             | 0        | ×         |  |

| MQP-80C-P01 | ×                                                             | ×        | 0         |  |

<sup>○ :</sup> Available × : Not available

Note: For more information about each package, see section "■ Package Dimensions."

<sup>\*2:</sup> Varies with conditions such as the operating frequency and the connected ICE. (See section "■ Electrical Characteristics.")

### **■ DIFFERENCES AMONG PRODUCTS**

### 1. Memory Size

Before evaluating using the piggyback product, verify its differences from the product that will actually be used. Take particular care on the following points:

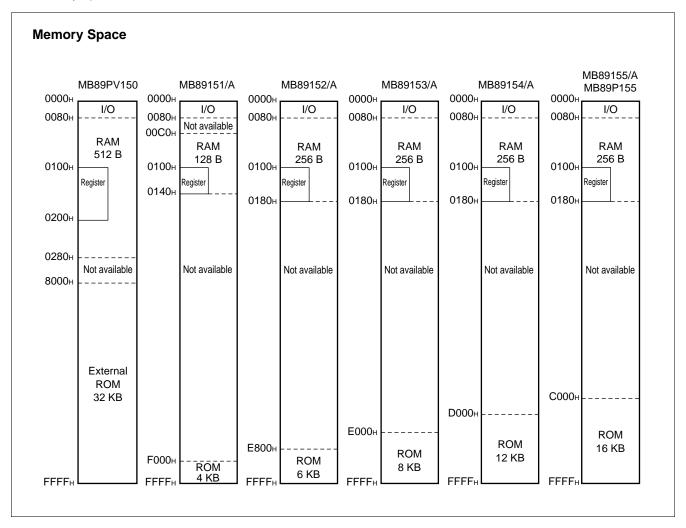

- On the MB89151/A, addresses 0140<sub>H</sub> and later of the register bank cannot be used. On the MB89152/A, 153/A, 154/A, 155/A, and MB89P155, addresses 0180<sub>H</sub> and later of each register bank cannot be used.

- On the MB89P155, addresses BFF0<sub>H</sub> to BFF6<sub>H</sub> comprise the option setting area, option settings can be read by reading these addresses.

- The stack area, etc., is set at the upper limit of the RAM.

#### 2. Current Consumption

- In the case of the MB89PV150, add the current consumed by the EPROM which is connected to the top socket.

- When operated at low speed, the product with an OTPROM (one-time PROM) or an EPROM will consume more current than the product with a mask ROM.

However, the current consumption in sleep/stop modes is the same. (For more information, see sections "■ Electrical Characteristics" and "■ Example Characteristics.")

### 3. Mask Options

Functions that can be selected as options and how to designate these options vary by the product.

Before using options check section "■ Mask Options."

Take particular care on the following point:

On the MB89PV150, options are fixed, except for the segment output selection.

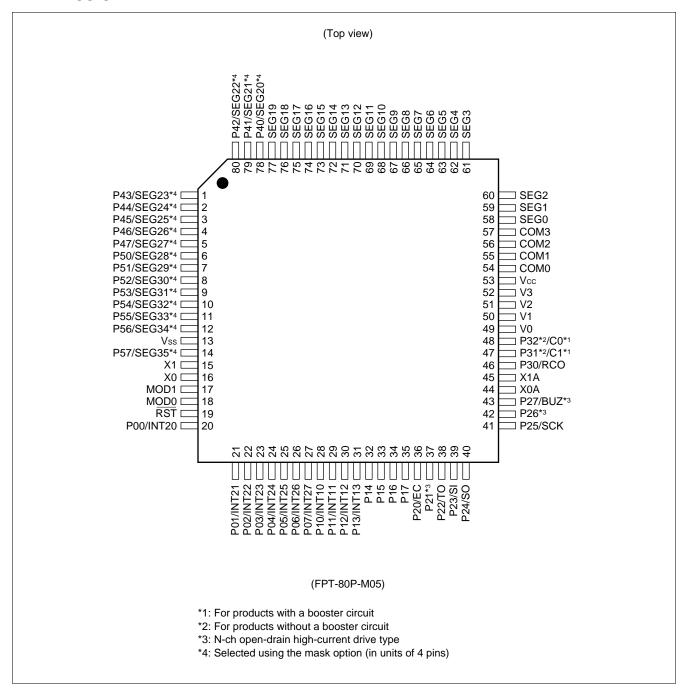

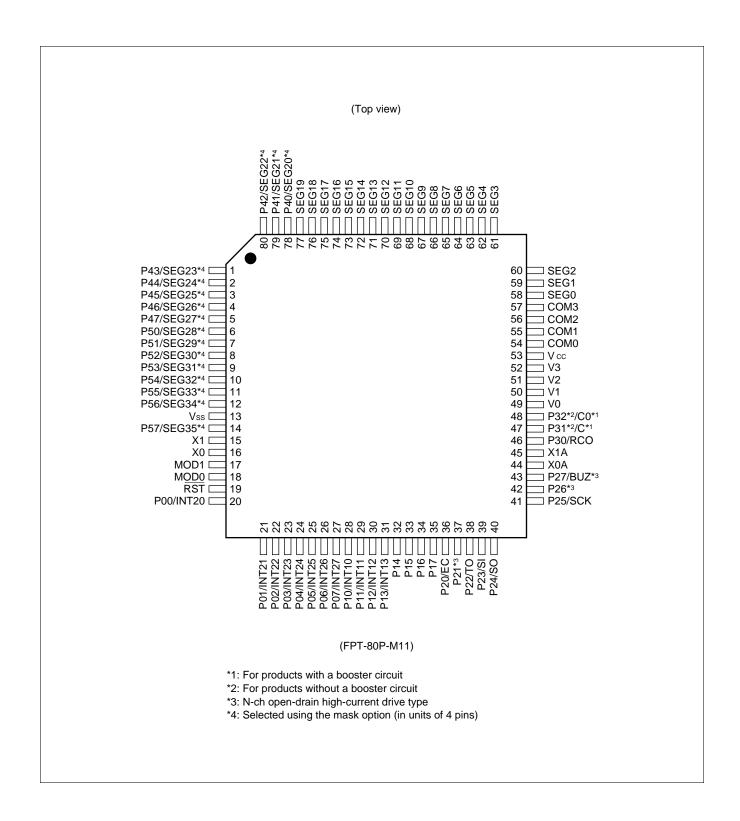

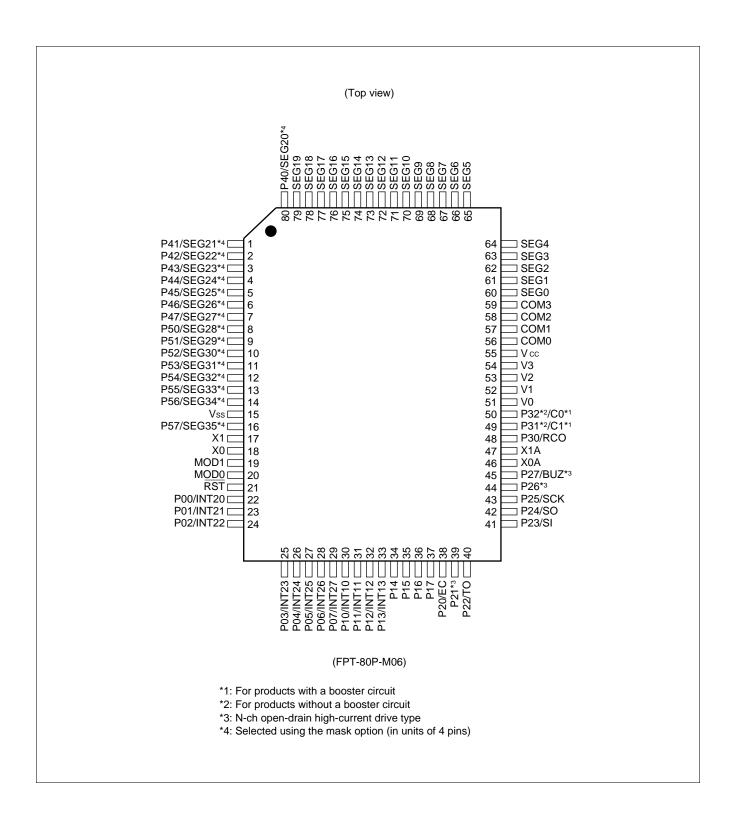

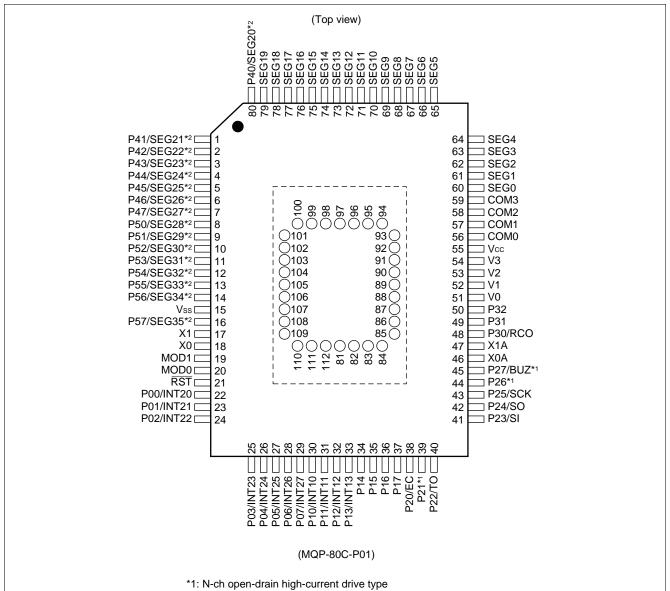

### **■ PIN ASSIGNMENT**

<sup>\*2:</sup> Selected using the mask option (in units of 4 pins).

#### · Pin assignment on package top

| Pin no. | Pin name        | Pin no. | Pin name | Pin no. | Pin name | Pin no. | Pin name |

|---------|-----------------|---------|----------|---------|----------|---------|----------|

| 81      | N.C.            | 89      | A2       | 97      | N.C.     | 105     | ŌĒ       |

| 82      | V <sub>PP</sub> | 90      | A1       | 98      | 04       | 106     | N.C.     |

| 83      | A12             | 91      | A0       | 99      | O5       | 107     | A11      |

| 84      | A7              | 92      | N.C.     | 100     | O6       | 108     | A9       |

| 85      | A6              | 93      | 01       | 101     | 07       | 109     | A8       |

| 86      | A5              | 94      | O2       | 102     | O8       | 110     | A13      |

| 87      | A4              | 95      | O3       | 103     | CE       | 111     | A14      |

| 88      | A3              | 96      | Vss      | 104     | A10      | 112     | Vcc      |

N.C.: Internally connected. Do not use.

## **■ PIN DESCRIPTION**

| Pin no.  |                 |                           | 0: :            |                                                                                                                                                                                                                                  |

|----------|-----------------|---------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP*1*3 | MQFP*4<br>QFP*2 | Pin name                  | Circuit<br>type | Function                                                                                                                                                                                                                         |

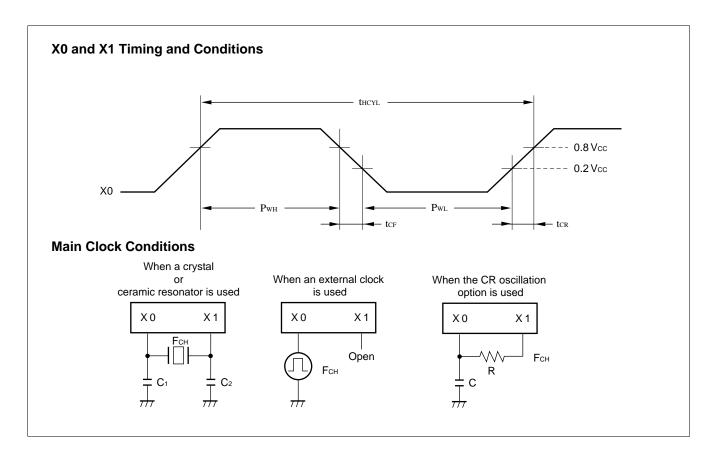

| 16       | 18              | X0                        | Α               | Main clock oscillator pins                                                                                                                                                                                                       |

| 15       | 17              | X1                        |                 |                                                                                                                                                                                                                                  |

| 18       | 20              | MOD0                      | С               | Operating mode selection pins                                                                                                                                                                                                    |

| 17       | 19              | MOD1                      |                 | Connect directly to Vss.                                                                                                                                                                                                         |

| 19       | 21              | RST                       | D               | Reset I/O pin This pin is an N-ch open-drain output type with a pull- up resistor and a hysteresis input type. "L" is output from this pin by an internal reset source. The internal circuit is initialized by the input of "L". |

| 20 to 27 | 22 to 29        | P00/INT20 to<br>P07/INT27 | Е               | General-purpose I/O ports Also serve as an external interrupt 2 input (wake-up function). External interrupt 2 input is hysteresis input.                                                                                        |

| 28 to 31 | 30 to 33        | P10/INT10 to<br>P13/INT13 | E               | General-purpose I/O ports Also serve as external interrupt 1 input. External interrupt 1 input is hysteresis input.                                                                                                              |

| 32 to 35 | 34 to 37        | P14 to P17                | F               | General-purpose I/O ports                                                                                                                                                                                                        |

| 36       | 38              | P20/EC                    | Н               | N-ch open-drain general-purpose I/O port<br>Also serves as the external clock input for the timer.<br>The peripheral is a hysteresis input type.                                                                                 |

| 37       | 39              | P21                       | I               | N-ch open-drain general-purpose I/O port                                                                                                                                                                                         |

| 38       | 40              | P22/TO                    | I               | N-ch open-drain general-purpose I/O port Also serves as a timer output.                                                                                                                                                          |

| 39       | 41              | P23/SI                    | Н               | N-ch open-drain general-purpose I/O port<br>Also serves as the data input for the 8-bit serial I/O.<br>The peripheral is a hysteresis input type.                                                                                |

| 40       | 42              | P24/SO                    | I               | N-ch open-drain general-purpose I/O port<br>Also serves as the data output for the 8-bit serial I/O.                                                                                                                             |

| 41       | 43              | P25/SCK                   | Н               | N-ch open-drain general-purpose I/O port<br>Also serves as the clock I/O for the 8-bit serial I/O.<br>The peripheral is a hysteresis input type.                                                                                 |

| 42       | 44              | P26                       | I               | N-ch open-drain general-purpose I/O port                                                                                                                                                                                         |

| 43       | 45              | P27/BUZ                   | I               | N-ch open-drain general-purpose I/O port<br>Also serves as a buzzer output.                                                                                                                                                      |

\*1: FPT-80P-M11

\*2: FPT-80P-M06

\*3: FPT-80P-M05

\*4: MQP-80C-P01

| Pin              | no.             |                                       | 0::             |                                                                                                                          |

|------------------|-----------------|---------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------|

| LQFP*1*3         | MQFP*4<br>QFP*2 | Pin name                              | Circuit<br>type | Function                                                                                                                 |

| 48               | 50              | P32                                   | J               | Functions as an N-ch open-drain general-purpose output port only in the products without a booster.                      |

|                  |                 | C0                                    | _               | Functions as a capacitor connection pin in the products with a booster.                                                  |

| 47               | 49              | P31                                   | J               | Functions as an N-ch open-drain general-purpose output port only in the products without a booster.                      |

|                  |                 | C1                                    | _               | Functions as a capacitor connection pin in the products with a booster.                                                  |

| 46               | 48              | P30/RCO                               | G               | General-purpose output-only port<br>Also serves as a remote control transmission output.                                 |

| 14               | 16              | P57/SEG35                             | J/K             | N-ch open-drain general-purpose output ports                                                                             |

| 12 to 6          | 14 to 8         | P56/SEG34 to<br>P50/SEG28             |                 | Also serve as LCD controller/driver segment output. Switching between port and common output is done by the mask option. |

| 5 to 1           | 7 to 3          | P47/SEG27 to<br>P43/SEG23             | J/K             |                                                                                                                          |

| 80,<br>79,<br>78 | 2,<br>1,<br>80  | P42/SEG22,<br>P41/SEG21,<br>P40/SEG20 |                 |                                                                                                                          |

| 77 to 58         | 79 to 60        | SEG19 to<br>SEG0                      | K               | LCD controller/driver segment output-only pins                                                                           |

| 57 to 54         | 59 to 56        | COM3 to COM0                          | K               | LCD controller/driver common output-only pins                                                                            |

| 52 to 49         | 54 to 51        | V3 to V0                              | _               | LCD driving power supply pins                                                                                            |

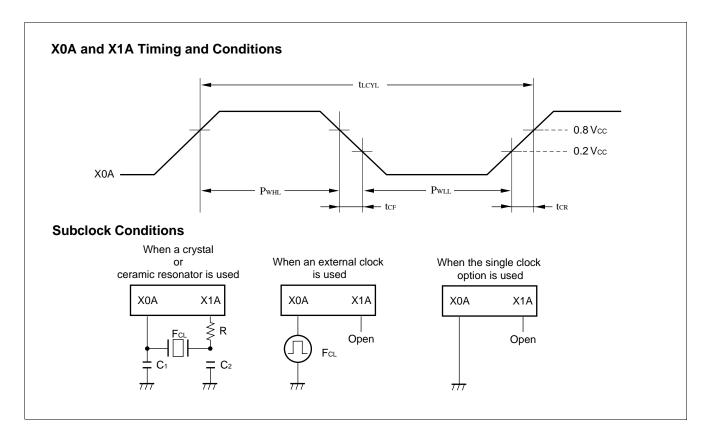

| 44               | 46              | X0A                                   | В               | Subclock crystal oscillator pins (32.768 kHz)                                                                            |

| 45               | 47              | X1A                                   |                 |                                                                                                                          |

| 53               | 55              | Vcc                                   | _               | Power supply pin                                                                                                         |

| 13               | 15              | Vss                                   | _               | Power supply (GND) pin                                                                                                   |

<sup>\*1:</sup> FPT-80P-M11

<sup>\*2:</sup> FPT-80P-M06

<sup>\*3:</sup> FPT-80P-M05

<sup>\*4:</sup> MQP-80C-P01

# • External EPROM pins (MB89PV150 only)

| Pin no.                                      | Pin name                                            | I/O | Function                                              |

|----------------------------------------------|-----------------------------------------------------|-----|-------------------------------------------------------|

| 82                                           | V <sub>PP</sub>                                     | 0   | "H" level output pin                                  |

| 83<br>84<br>85<br>86<br>87<br>88<br>89<br>90 | A12<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0 | 0   | Address output pins                                   |

| 93<br>94<br>95                               | O1<br>O2<br>O3                                      | I   | Data input pins                                       |

| 96                                           | Vss                                                 | 0   | Power supply (GND) pin                                |

| 98<br>99<br>100<br>101<br>102                | O4<br>O5<br>O6<br>O7<br>O8                          | I   | Data input pins                                       |

| 103                                          | CE                                                  | 0   | ROM chip enable pin Outputs "H" during standby.       |

| 104                                          | A10                                                 | 0   | Address output pin                                    |

| 105                                          | ŌE                                                  | 0   | ROM output enable pin<br>Outputs "L" at all times.    |

| 107<br>108<br>109                            | A11<br>A9<br>A8                                     | 0   | Address output pins                                   |

| 110                                          | A13                                                 | 0   |                                                       |

| 111                                          | A14                                                 | 0   |                                                       |

| 112                                          | Vcc                                                 | 0   | EPROM power supply pin                                |

| 81<br>92<br>97<br>106                        | N.C.                                                | _   | Internally connected pins Be sure to leave them open. |

## ■ I/O CIRCUIT TYPE

| Туре | Circuit                                                                                                                                | Remarks                                                                                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| A    | X1<br>X0<br>X0<br>X0<br>X1<br>X0<br>X1<br>X0<br>X1<br>X0<br>X1<br>X1<br>X1<br>X1<br>X1<br>X1<br>X1<br>X1<br>X1<br>X1<br>X1<br>X1<br>X1 | Crystal or ceramic oscillation type (main clock)  • At an oscillation feedback resistor of approximately 1 MΩ/5.0 V                    |

|      | X1<br>X0<br>X0<br>X0<br>Standby control signal                                                                                         | CR oscillation type (main clock) (except MB89PV150/P155)                                                                               |

| В    | X1A<br>X0A<br>X0A<br>Standby control signal                                                                                            | Crystal oscillation type (subclock) • At an oscillation feedback resistor of approximately 4.5 MΩ/3.0 V                                |

| С    |                                                                                                                                        |                                                                                                                                        |

| D    | R<br>P-ch<br>N-ch                                                                                                                      | <ul> <li>At output pull-up resistor (P-ch) of approximately 50 kΩ/5.0 V</li> <li>Hysteresis input</li> </ul>                           |

| E    | P-ch N-ch Port Peripheral                                                                                                              | <ul> <li>CMOS I/O</li> <li>The peripheral is a hysteresis input type.</li> <li>Pull-up resistor optional (except MB89PV150)</li> </ul> |

| Type | Circuit                      | Remarks                                                                                                                                                                          |

|------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F    | R P-ch N-ch                  | CMOS I/O  Pull-up resistor optional (except MB89PV150)                                                                                                                           |

| G    | P-ch<br>N-ch                 | <ul> <li>CMOS output</li> <li>P-ch output is a high-current drive type.</li> </ul>                                                                                               |

| Н    | P-ch N-ch Port Peripheral    | <ul> <li>N-ch open-drain I/O</li> <li>CMOS input</li> <li>The peripheral is a hysteresis input type.</li> <li>Pull-up resistor optional (except MB89PV150/P155)</li> </ul>       |

| I    | P-ch<br>N-ch                 | <ul> <li>N-ch open-drain I/O</li> <li>CMOS input</li> <li>P21, P26, and P27 are a high-current drive type.</li> <li>Pull-up resistor optional (except MB89PV150/P155)</li> </ul> |

| J    | P-ch<br>N-ch                 | <ul> <li>N-ch open-drain output</li> <li>Pull-up resistor optional (except MB89PV150/P155)</li> <li>P31 and P32 are not provided with a pull-up resistor.</li> </ul>             |

| К    | P-ch<br>N-ch<br>P-ch<br>N-ch | LCD controller/driver segment output                                                                                                                                             |

### **■ HANDLING DEVICES**

### 1. Preventing Latchup

Latchup may occur on CMOS ICs if voltage higher than V<sub>CC</sub> or lower than V<sub>SS</sub> is applied to input and output pins other than medium- to high-voltage pins or if higher than the voltage which shows on "1. Absolute Maximum Ratings" in section "■ Electrical Characteristics" is applied between V<sub>CC</sub> and V<sub>SS</sub>.

When latchup occurs, power supply current increases rapidly and might thermally damage elements. When using, take great care not to exceed the absolute maximum ratings.

Also, take care to prevent the analog power supply (AVcc and AVR) and analog input from exceeding the digital power supply (Vcc) when the analog system power supply is turned on and off.

#### 2. Treatment of Unused Input Pins

Leaving unused input pins open could cause malfunctions. They should be connected to a pull-up or pull-down resistor.

### 3. Treatment of Power Supply Pins on Microcontrollers with A/D and D/A Converters

Connect to be AVcc = DAVC = Vcc and AVss = AVR = Vss even if the A/D and D/A converters are not in use.

#### 4. Treatment of N.C. Pins

Be sure to leave (internally connected) N.C. pins open.

#### 5. Power Supply Voltage Fluctuations

Although  $V_{\rm CC}$  power supply voltage is assured to operate within the rated range, a rapid fluctuation of the voltage could cause malfunctions, even if it occurs within the rated range. Stabilizing voltage supplied to the IC is therefore important. As stabilization guidelines, it is recommended to control power so that  $V_{\rm CC}$  ripple fluctuations (P-P value) will be less than 10% of the standard  $V_{\rm CC}$  value at the commercial frequency (50 to 60 Hz) and the transient fluctuation rate will be less than 0.1 V/ms at the time of a momentary fluctuation such as when power is switched.

#### 6. Precautions when Using an External Clock

Even when an external clock is used, oscillation stabilization time is required for power-on reset (optional) and wake-up from stop mode.

### ■ PROGRAMMING TO THE EPROM ON THE MB89P155

The MB89P155 is an OTPROM version of the MB89150/A series.

### 1. Features

- 16-Kbyte PROM on chip

- Options can be set using the EPROM programmer.

- Equivalency to the MBM27C256A in EPROM mode (when programmed with the EPROM programmer)

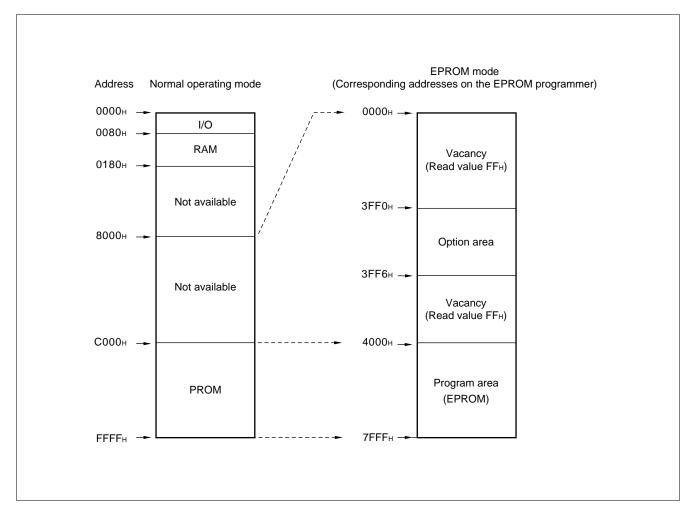

### 2. Memory Space

Memory space in the EPROM mode is diagrammed below.

## 3. Programming to the EPROM

In EPROM mode, the MB89P155 functions equivalent to the MBM27C256A. This allows the PROM to be programmed with a general-purpose EPROM programmer (the electronic signature mode cannot be used) by using the dedicated socket adapter.

### • Programming procedure

- (1) Set the EPROM programmer to the MBM27C256A.

- (2) Load program data into the EPROM programmer at 4000<sub>H</sub> to 7FFF<sub>H</sub> (note that addresses C000<sub>H</sub> to FFFF<sub>H</sub> while operating as a normal operating mode assign to 4000<sub>H</sub> to 7FFF<sub>H</sub> in EPROM mode).

Load option data into addresses 3FF0<sub>H</sub> to 3FF5<sub>H</sub> of the EPROM programmer. (For information about each corresponding option, see "7. Setting OTPROM Options.")

- (3) Program with the EPROM programmer.

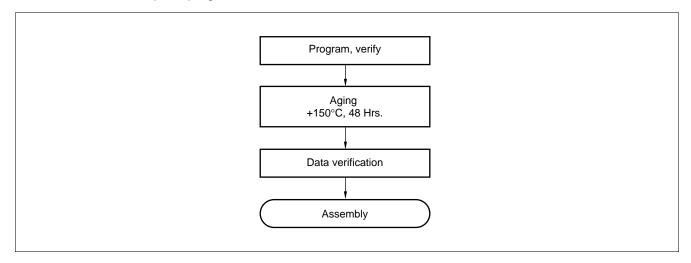

### 4. Recommended Screening Conditions

High-temperature aging is recommended as the pre-assembly screening procedure for a product with a blanked OTPROM microcomputer program.

### 5. Programming Yield

All bits cannot be programmed at Fujitsu shipping test to a blanked OTPROM microcomputer, due to its nature. For this reason, a programming yield of 100% cannot be assured at all times.

### 6. EPROM Programmer Socket Adapter

| Package     | Compatible socket adapter |

|-------------|---------------------------|

| FPT-80P-M05 | ROM-80SQF-28DP-8L         |

| FPT-80P-M06 | ROM-80QF-28DP-8L3         |

| FPT-80P-M11 | ROM-80QF2-28DP-8L2        |

Inquiry: Sun Hayato Co., Ltd.: TEL 81-3-3802-5760

## 7. Setting OTPROM Options

The programming procedure is the same as that for the PROM. Options can be set by programming values at the addresses shown on the memory map. The relationship between bits and options is shown on the following bit map:

### • OTPROM option bit map

|        | Bit 7               | Bit 6               | Bit 5                                               | Bit 4                               | Bit 3               | Bit 2                                  | Bit 1                                                       | Bit 0                                |

|--------|---------------------|---------------------|-----------------------------------------------------|-------------------------------------|---------------------|----------------------------------------|-------------------------------------------------------------|--------------------------------------|

| 3FF0⊦  | Vacancy<br>Readable | Vacancy<br>Readable | Oscillation sta<br>WTM1<br>See section<br>Options." | abilization time<br>WTM0<br>"■ Mask | Vacancy<br>Readable | Reset pin<br>output<br>1: Yes<br>0: No | Clock mode<br>selection<br>1: Dual clock<br>0: Single clock | Power-on<br>reset<br>1: Yes<br>0: No |

| 3FF1н  | P07                 | P06                 | P05                                                 | P04                                 | P03                 | P02                                    | P01                                                         | P00                                  |

|        | Pull-up             | Pull-up             | Pull-up                                             | Pull-up                             | Pull-up             | Pull-up                                | Pull-up                                                     | Pull-up                              |

|        | 1: No               | 1: No               | 1: No                                               | 1: No                               | 1: No               | 1: No                                  | 1: No                                                       | 1: No                                |

|        | 0: Yes              | 0: Yes              | 0: Yes                                              | 0: Yes                              | 0: Yes              | 0: Yes                                 | 0: Yes                                                      | 0: Yes                               |

| 3FF2н  | P17                 | P16                 | P15                                                 | P14                                 | P13                 | P12                                    | P11                                                         | P10                                  |

|        | Pull-up             | Pull-up             | Pull-up                                             | Pull-up                             | Pull-up             | Pull-up                                | Pull-up                                                     | Pull-up                              |

|        | 1: No               | 1: No               | 1: No                                               | 1: No                               | 1: No               | 1: No                                  | 1: No                                                       | 1: No                                |

|        | 0: Yes              | 0: Yes              | 0: Yes                                              | 0: Yes                              | 0: Yes              | 0: Yes                                 | 0: Yes                                                      | 0: Yes                               |

| 3FF3н  | Vacancy             | Vacancy             | Vacancy                                             | Vacancy                             | Vacancy             | Vacancy                                | Vacancy                                                     | Vacancy                              |

|        | Readable            | Readable            | Readable                                            | Readable                            | Readable            | Readable                               | Readable                                                    | Readable                             |

| 3FF4⊦ı | Vacancy             | Vacancy             | Vacancy                                             | Vacancy                             | Vacancy             | Vacancy                                | Vacancy                                                     | Vacancy                              |

|        | Readable            | Readable            | Readable                                            | Readable                            | Readable            | Readable                               | Readable                                                    | Readable                             |

| 3FF5⊦  | Vacancy             | Vacancy             | Vacancy                                             | Vacancy                             | Vacancy             | Vacancy                                | Vacancy                                                     | Vacancy                              |

|        | Readable            | Readable            | Readable                                            | Readable                            | Readable            | Readable                               | Readable                                                    | Readable                             |

Notes: • Set each bit to 1 to erase.

• Do not write 0 to the vacant bit.

The read value of the vacant bit is 1, unless 0 is written to it.

## ■ PROGRAMMING TO THE EPROM WITH PIGGYBACK/EVALUATION DEVICE

#### 1. EPROM for Use

MBM27C256A-20TV

### 2. Programming Socket Adapter

To program to the PROM using an EPROM programmer, use the socket adapter (manufacturer: Sun Hayato Co., Ltd.) listed below.

| Package           | Adapter socket part number |

|-------------------|----------------------------|

| LCC-32(Rectangle) | ROM-32LC-28DP-YG           |

| LCC-32(Square)    | ROM-32LC-28DP-S            |

Inquiry: Sun Hayato Co., Ltd.: TEL 81-3-3802-5760

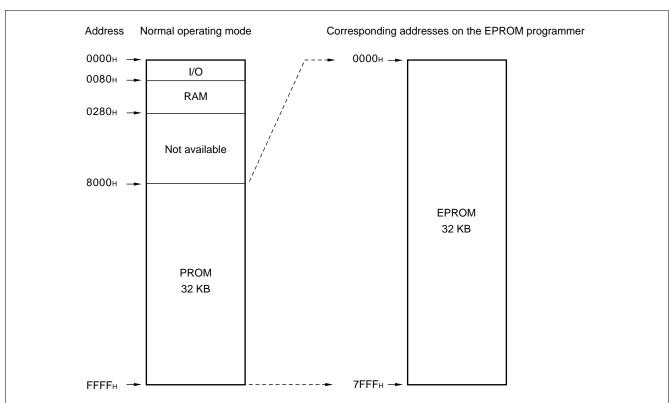

### 3. Memory Space

Memory space in each mode is diagrammed below.

### 4. Programming to the EPROM

- (1) Set the EPROM programmer to the MBM27C256A.

- (2) Load program data into the EPROM programmer at 4000<sub>H</sub> to 7FFF<sub>H</sub>.

- (3) Program to 0000 H to 7FFFH with the EPROM programmer.

### **■ BLOCK DIAGRAM**

### **■ CPU CORE**

## 1. Memory Space

The microcontrollers of the MB89150/A series offer a memory space of 64 Kbytes for storing all of I/O, data, and program areas. The I/O area is located at the lowest address. The data area is provided immediately above the I/O area. The data area can be divided into register, stack, and direct areas according to the application. The program area is located at exactly the opposite end, that is, near the highest address. Provide the tables of interrupt reset vectors and vector call instructions toward the highest address within the program area. The memory space of the MB89150/A series is structured as illustrated below.

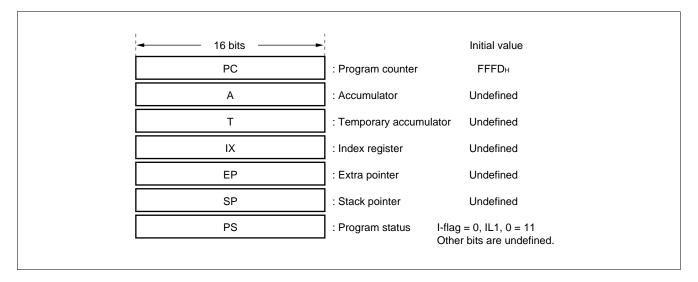

## 2. Registers

The F<sup>2</sup>MC-8L family has two types of registers; dedicated registers in the CPU and general-purpose registers in the memory. The following dedicated registers are provided:

Program counter (PC): A 16-bit register for indicating instruction storage positions

Accumulator (A): A 16-bit temporary register for storing arithmetic operations, etc. When the

instruction is an 8-bit data processing instruction, the lower byte is used.

Temporary accumulator (T): A 16-bit register which performs arithmetic operations with the accumulator

When the instruction is an 8-bit data processing instruction, the lower byte is used.

Index register (IX): A 16-bit register for index modification

Extra pointer (EP): A 16-bit pointer for indicating a memory address

Stack pointer (SP): A 16-bit register for indicating a stack area

Program status (PS): A 16-bit register for storing a register pointer, a condition code

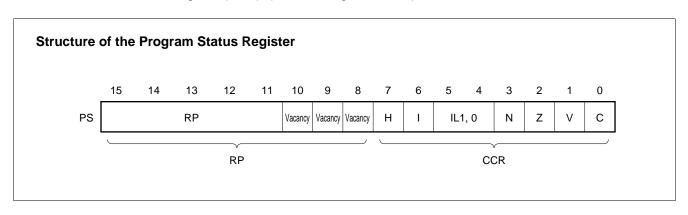

The PS can further be divided into higher 8 bits for use as a register bank pointer (RP) and the lower 8 bits for use as a condition code register (CCR). (See the diagram below.)

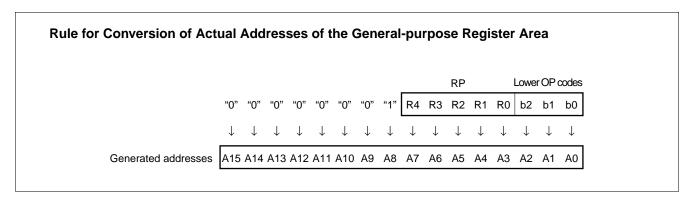

The RP indicates the address of the register bank currently in use. The relationship between the pointer contents and the actual address is based on the conversion rule illustrated below.

The CCR consists of bits indicating the results of arithmetic operations and the contents of transfer data and bits for control of CPU operations at the time of an interrupt.

H-flag: Set when a carry or a borrow from bit 3 to bit 4 occurs as a result of an arithmetic operation. Cleared otherwise. This flag is for decimal adjustment instructions.

I-flag: Interrupt is allowed when this flag is set to 1. Interrupt is prohibited when the flag is set to 0. Set to 0 when reset.

IL1, 0: Indicates the level of the interrupt currently allowed. Processes an interrupt only if its request level is higher than the value indicated by this bit.

| IL1 | IL0 | Interrupt level | High-low           |

|-----|-----|-----------------|--------------------|

| 0   | 0   | 1               | High               |

| 0   | 1   | l               | <b>†</b>           |

| 1   | 0   | 2               |                    |

| 1   | 1   | 3               | Low = no interrupt |

N-flag: Set if the MSB is set to 1 as the result of an arithmetic operation. Cleared when the bit is set to 0.

Z-flag: Set when an arithmetic operation results in 0. Cleared otherwise.

V-flag: Set if the complement on 2 overflows as a result of an arithmetic operation. Reset if the overflow does not occur.

C-flag: Set when a carry or a borrow from bit 7 occurs as a result of an arithmetic operation. Cleared otherwise. Set to the shift-out value in the case of a shift instruction.

The following general-purpose registers are provided:

General-purpose registers: An 8-bit register for storing data

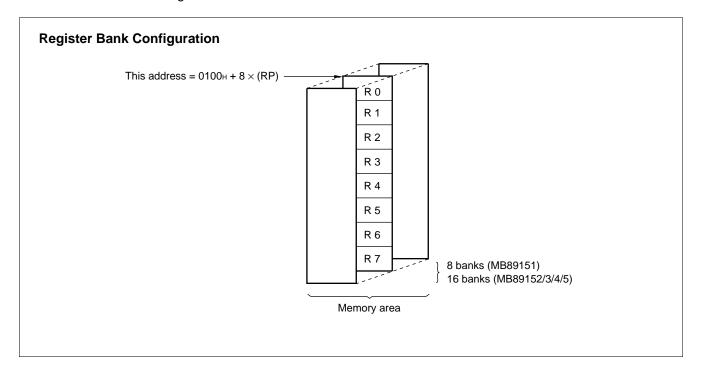

The general-purpose registers are 8 bits and located in the register banks of the memory. One bank contains eight registers. Up to a total of 8 banks can be used on the MB89151 (RAM  $128 \times 8$  bits), and a total of 16 banks can be used on the MB89152/3/4/5 (RAM  $256 \times 8$  bits). The bank currently in use is indicated by the register bank pointer (RP).

Note: The number of register banks that can be used varies with the RAM size.

## ■ I/O MAP

| Address    | Read/write | Register name             | Register description                   |  |  |

|------------|------------|---------------------------|----------------------------------------|--|--|

| 00н        | (R/W)      | PDR0                      | Port 0 data register                   |  |  |

| 01н        | (W)        | DDR0                      | Port 0 data direction register         |  |  |

| 02н        | (R/W)      | PDR1                      | Port 1 data register                   |  |  |

| 03н        | (W)        | DDR1                      | Port 1 data direction register         |  |  |

| 04н        | (R/W)      | PDR2                      | Port 2 data register                   |  |  |

| 05н        | (W)        | DDR2                      | Port 2 data direction register         |  |  |

| 06н        |            |                           | Vacancy                                |  |  |

| 07н        | (R/W)      | SYCC                      | System clock control register          |  |  |

| 08н        | (R/W)      | STBC                      | Standby control register               |  |  |

| 09н        | (R/W)      | WDTC                      | Watchdog timer control register        |  |  |

| ОАн        | (R/W)      | TBTC                      | Time-base timer control register       |  |  |

| 0Вн        | (R/W)      | WPCR                      | Watch prescaler control register       |  |  |

| 0Сн        | (R/W)      | PDR3                      | Port 3 data register                   |  |  |

| ОДн        |            |                           | Vacancy                                |  |  |

| 0Ен        | (R/W)      | PDR4                      | Port 4 data register                   |  |  |

| 0Fн        | (R/W)      | PDR5                      | Port 5 data register                   |  |  |

| 10н        | (R/W)      | BZCR                      | Buzzer register                        |  |  |

| 11н        |            |                           | Vacancy                                |  |  |

| 12н        |            |                           | Vacancy                                |  |  |

| 13н        |            |                           | Vacancy                                |  |  |

| 14н        | (R/W)      | RCR1                      | Remote control transmission register 1 |  |  |

| 15н        | (R/W)      | RCR2                      | Remote control transmission register 2 |  |  |

| 16н        |            |                           | Vacancy                                |  |  |

| 17н        |            |                           | Vacancy                                |  |  |

| 18н        | (R/W)      | T2CR                      | Timer 2 control register               |  |  |

| 19н        | (R/W)      | T1CR                      | Timer 1 control register               |  |  |

| 1Ан        | (R/W)      | T2DR                      | Timer 2 data register                  |  |  |

| 1Вн        | (R/W)      | T1DR                      | Timer 1 data register                  |  |  |

| 1Сн        | (R/W)      | SMR1                      | Serial mode register                   |  |  |

| 1Dн        | (R/W)      | SDR1 Serial data register |                                        |  |  |

| 1Ен to 2Fн |            |                           | Vacancy                                |  |  |

# (Continued)

| Address     | Read/write | Register name | Register description                     |

|-------------|------------|---------------|------------------------------------------|

| 30н         | (R/W)      | EIE1          | External interrupt 1 enable register     |

| 31н         | (R/W)      | EIF1          | External interrupt 1 flag register       |

| 32н         | (R/W)      | EIE2          | External interrupt 2 enable register     |

| 33н         | (R/W)      | EIF2          | External interrupt 2 flag register       |

| 34н to 5Fн  |            |               | Vacancy                                  |

| 60н to 71н  | (R/W)      | VRAM          | Display data RAM                         |

| 72н         | (R/W)      | LCR1          | LCD controller/driver control register 1 |

| 73н to 7Вн  |            |               | Vacancy                                  |

| 7Сн         | (W)        | ILR1          | Interrupt level setting register 1       |

| 7Dн         | (W)        | ILR2          | Interrupt level setting register 2       |

| 7Ен         | (W)        | ILR3          | Interrupt level setting register 3       |

| <b>7</b> Fн |            |               | Vacancy                                  |

Note: Do not use vacancies.

## **■ ELECTRICAL CHARACTERISTICS**

# 1. Absolute Maximum Ratings

( Vss = 0.0 V)

| Danamatan                              | Cymphol          | Va        | lue       | l lm!4 | Damarka                                                                                                                          |

|----------------------------------------|------------------|-----------|-----------|--------|----------------------------------------------------------------------------------------------------------------------------------|

| Parameter                              | Symbol           | Min.      | Max.      | Unit   | Remarks                                                                                                                          |

| Power supply voltage                   | Vcc              | Vss-0.3   | Vss + 7.0 | V      |                                                                                                                                  |

| LCD power supply voltage               | V0 to V3         | Vss-0.3   | Vss + 7.0 | V      | V0 to V3 pins on the product with booster                                                                                        |

| LCD power supply voltage               | V0 10 V3         | Vss - 0.3 | Vcc + 0.3 | V      | V0 to V3 pins on the product without booster                                                                                     |

| Input voltage                          | Vıı              | Vss - 0.3 | Vcc + 0.3 | V      | V <sub>I1</sub> must not exceed V <sub>SS</sub> +7.0 V.<br>All pins except P20 to P27<br>without a pull-up resistor              |

|                                        | Vı2              | Vss - 0.3 | Vss + 7.0 | V      | P20 to P27 without a pull-up resistor                                                                                            |

| Output voltage                         | V <sub>01</sub>  | Vss-0.3   | Vcc + 0.3 | V      | Vo1 must not exceed Vss +7.0 V.<br>All pins except P20 to P27, P31,<br>P32, P40 to P47, P50 to P57<br>without a pull-up resistor |

| . •                                    | Vo <sub>2</sub>  | Vss-0.3   | Vss + 7.0 | V      | P20 to P27, P31, P32, P40 to P47, and P50 to P57, without a pull-up resistor                                                     |

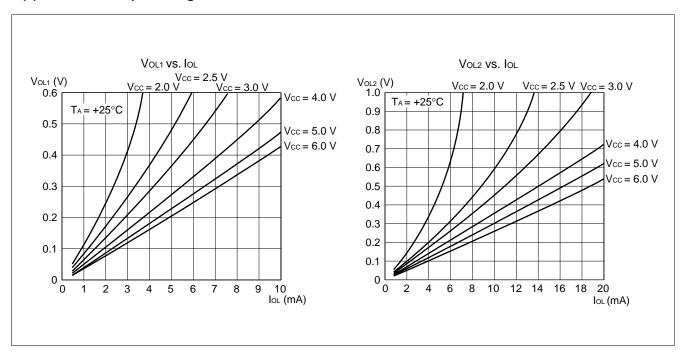

| "L" level maximum output               | l <sub>OL1</sub> | _         | 10        | mA     | All pins except P21, P26, P27, and power supply pins                                                                             |

| Current                                | lo <sub>L2</sub> | _         | 20        | mA     | P21, P26, and P27                                                                                                                |

| "L" level average output current       | lolav1           | _         | 4         | mA     | Average value (operating current × operating rate) All pins except P21, P26, P27, and power supply pins.                         |

|                                        | lolav2           | _         | 8         | mA     | Average value (operating current × operating rate) P21, P26, and P27                                                             |

| "L" level total maximum output current | ΣΙοι             | _         | 80        | mA     |                                                                                                                                  |

| "L" level total average output current | $\Sigma$ lolav   | _         | 40        | mA     | Average value (operating current × operating rate)                                                                               |

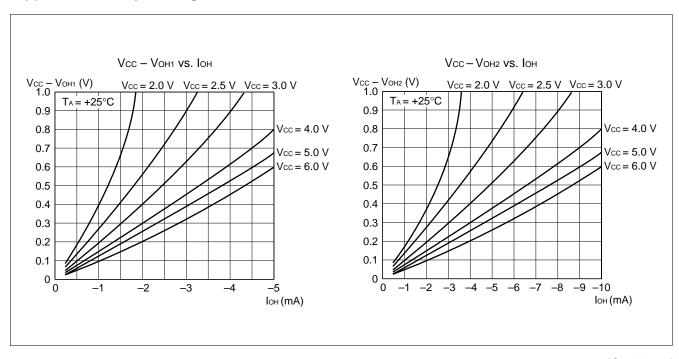

| "H" level maximum output current       | <b>І</b> он1     | _         | -5        | mA     | All pins except P30 and power supply pins                                                                                        |

| Curent                                 | <b>I</b> OH2     | _         | -10       | mA     | P30                                                                                                                              |

(Continued)

(Vss = 0.0 V)

| Parameter                              | Symbol         | Va          | lue  | Unit  | Remarks                                                                                       |  |

|----------------------------------------|----------------|-------------|------|-------|-----------------------------------------------------------------------------------------------|--|

| Parameter                              | Syllibol       | Min.        | Max. | Ullit | itelliaiks                                                                                    |  |

| "H" level average output current       | Iонаv1         | _           | -2   | mA    | Average value (operating current × operating rate) All pins except P30 and power supply pins. |  |

|                                        | loнav2         | _           | -4   | mA    | Average value (operating current × operating rate) P30                                        |  |

| "H" level total output current         | ∑Іон           | _           | -20  | mA    |                                                                                               |  |

| "H" level total average output current | ΣΙοнаν         | _           | -10  | mA    | Average value (operating current × operating rate)                                            |  |

| Power consumption                      | P <sub>D</sub> | _           | 300  | mW    |                                                                                               |  |

| Operating temperature                  | TA             | -40         | +85  | °C    |                                                                                               |  |

| Storage temperature                    | Tstg           | <b>-</b> 55 | +150 | °C    |                                                                                               |  |

Precautions: Permanent device damage may occur if the above "Absolute Maximum Ratings" are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## 2. Recommended Operating Conditions

(Vss = 0.0 V)

| Damamatan                                | Cumbal   | Va    | lue   | Unit  | Remarks                                                                             |  |  |

|------------------------------------------|----------|-------|-------|-------|-------------------------------------------------------------------------------------|--|--|

| Parameter                                | Symbol   | Min.  | Max.  | Ullit | Remarks                                                                             |  |  |

|                                          |          | 2.2*1 | 6.0   | V     | Normal operation assurance range<br>Single clock system of the mask<br>ROM product. |  |  |

| Power supply voltage                     | Vcc      | 2.2*1 | 4.0   | V     | Normal operation assurance range<br>Dual-clock system of the mask ROM<br>product.   |  |  |

|                                          |          | 2.7*1 | 6.0   | V     | MB89P155/PV150                                                                      |  |  |

|                                          |          | 1.5   | 6.0   | V     | Retains the RAM state in stop mode                                                  |  |  |

| LCD power supply voltage                 | V0 to V3 | Vss   | Vcc*2 | V     | V0 to V3 pins                                                                       |  |  |

| LCD reference power supply input voltage | VIR      | 1.3   | 2.2   | V     | V1 pin on the products with a booster<br>Reference power external input             |  |  |

| Operating temperature                    | TA       | -40   | +85   | °C    |                                                                                     |  |  |

<sup>\*1:</sup> The minimum operating power supply voltage varies with the execution time (instruction cycle time) setting for the operating frequency.

<sup>\*2:</sup> The LCD power supply voltage range and optimum value vary depending on the characteristics of the liquidcrystal display element.

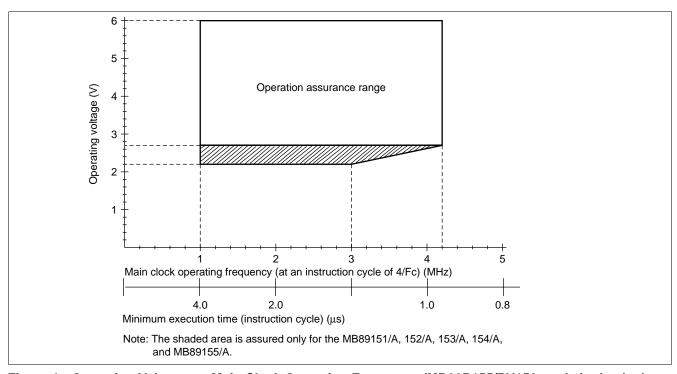

Figure 1 Operating Voltage vs. Main Clock Operating Frequency (MB89P155/PV150, and single-clock MB89151/A, 152/A, 153/A, 154/A, and MB89155/A)

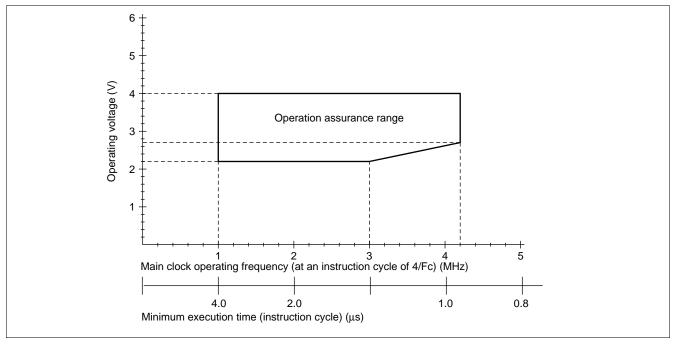

Figure 2 Operating Voltage vs. Main Clock Operating Frequency (Dual-clock MB89151/A, 152/A, 153/A, 154/A, and MB89155/A)

Figures 1 and 2 indicate the operating frequency of the external oscillator at a minimum execution time of 4/FcH.

Since the operating voltage range is dependent on the minimum execution time, see the minimum execution time if the operating speed is switched using a gear.

## 3. DC Characteristics

$(Vcc = +5.0 \text{ V}, Vss = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

|                                           |                  |                                                                                      |                            | ( • • • | , v33 – 0.0 | V, IA       | $A = -40^{\circ}C$ to $+85^{\circ}C$ |                                       |

|-------------------------------------------|------------------|--------------------------------------------------------------------------------------|----------------------------|---------|-------------|-------------|--------------------------------------|---------------------------------------|

| Parameter                                 | Symbol           | Pin                                                                                  | Condition                  | Min     | Value       | Max         | Unit                                 | Remarks                               |

|                                           |                  |                                                                                      |                            | Min.    | Тур.        | Max.        |                                      |                                       |

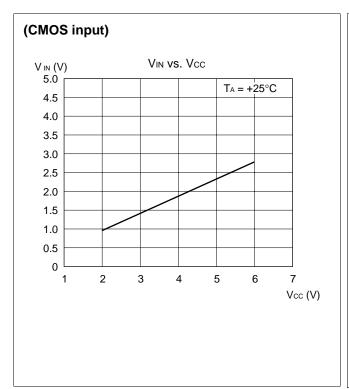

| "Ll" lovel input                          | VIH              | P00 to P07,<br>P10 to P17,<br>P20 to P27                                             | 7,                         |         | _           | Vcc + 0.3   | V                                    | CMOS input                            |

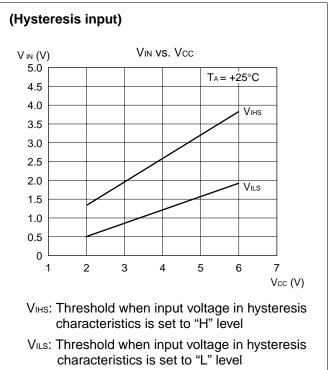

| "H" level input<br>voltage                | VIHS             | RST, MOD0, MOD1,<br>EC, SI, SCK,<br>INT10 to INT13,<br>INT20 to INT27                |                            | 0.8 Vcc |             | Vss + 0.3   | V                                    | Hysteresis input                      |

|                                           | VIL              | P00 to P07, P10 to P17,<br>P20 to P27                                                | _                          | Vss-0.3 |             | 0.3 Vcc     | V                                    | CMOS input                            |

| "L" level input<br>voltage                | VILS             | RST, MOD0, MOD1,<br>EC, SI, SCK,<br>INT10 to INT13,<br>INT20 to INT27                |                            | Vss-0.3 | _           | 0.2 Vcc     | V                                    | Hysteresis input                      |

| Open-drain output pin application voltage | VD               | P20 to P27, P31, P32,<br>P40 to P47, P50 to P57                                      |                            | Vss-0.3 |             | Vss + 6.0*1 | V                                    | Without pull-up resistor              |

| "H" level output                          | V <sub>OH1</sub> | P00 to P07, P10 to P17                                                               | Iон = −2.0 mA              | 2.4     | _           |             | V                                    |                                       |

| voltage                                   | V <sub>OH2</sub> | P30                                                                                  | $I_{OH} = -6.0 \text{ mA}$ | 4.0     | _           | _           | V                                    |                                       |

| "L" level output voltage                  | V <sub>OL1</sub> | P00 to P07, P10 to P17,<br>P20, P22 to P25,<br>P30 to P32, P40 to P47,<br>P50 to P57 | IoL = 1.8 mA               | _       | _           | 0.4         | ٧                                    |                                       |

| Voltage                                   | V <sub>OL2</sub> | P21, P26, P27                                                                        | IoL = 8.0 mA               | _       | _           | 0.4         | V                                    |                                       |

|                                           | V <sub>OL3</sub> | RST                                                                                  | IoL = 4.0 mA               | _       | _           | 0.4         | V                                    |                                       |

| Input leakage current                     | ILI1             | MOD0, MOD1, P30,<br>P00 to P07, P10 to P17                                           | 0.0 V < V1 < Vcc           | _       | _           | ±5          | μΑ                                   | Without pull-up resistor              |

| (Hi-z output<br>leakage current)          | I <sub>LI2</sub> | P20 to P27, P31, P32,<br>P40 to P47, P50 to P57                                      | 0.0 V < V1 < 6.0 V         | _       | _           | ±1          | μΑ                                   | Without pull-up resistor              |

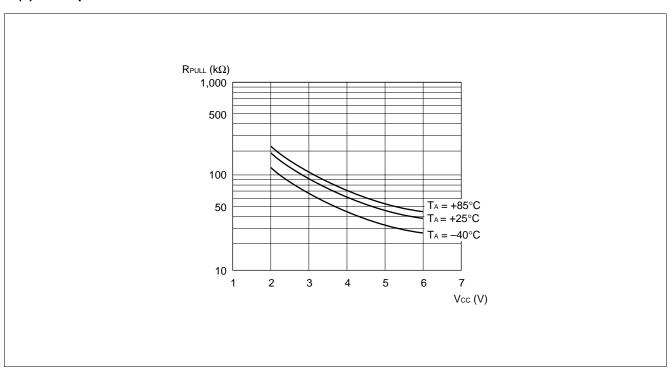

| Pull-up resistance                        | Rpull            | P00 to P07, P10 to P17,<br>P20 to P27, P40 to P47,<br>P50 to P57, RST                | V1 = 0.0 V                 | 25      | 50          | 100         | kΩ                                   | With pull-up resistor                 |

| Common output impedance                   | Rvсом            | COM0 to COM3                                                                         | V1 to V3 = 5.0 V           | _       | _           | 2.5         | kΩ                                   |                                       |

| Segment output impedance                  | Rvseg            | SEG0 to SEG35                                                                        | V1 to V3 = 5.0 V           | _       | _           | 15          | kΩ                                   |                                       |

| LCD divided resistance                    | RLCD             | _                                                                                    | Between<br>Vcc and V0      | 300     | 500         | 750         | kΩ                                   | Products<br>without a<br>booster only |

| LCD leakage current                       | ILCDL            | V0 to V3,<br>COM0 to COM3,<br>SEG0 to SEG35                                          | _                          | _       | _           | ±1          | μΑ                                   |                                       |

$(Vcc = +5.0 \text{ V}, Vss = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

|                                          |                  |     |                                                                                                                                                                                                                   | (۷0  | Value | vss = 0.0 | V, IA | $= -40^{\circ}$ C to $+85^{\circ}$ C)                                    |

|------------------------------------------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------|-------|--------------------------------------------------------------------------|

| Parameter                                | Symbol           | Pin | Condition                                                                                                                                                                                                         | Min. | Тур.  | Max.      | Unit  | Remarks                                                                  |

| Booster for LCD                          | V <sub>OV3</sub> | V3  |                                                                                                                                                                                                                   | 4.3  | 4.5   | 4.7       | V     |                                                                          |

| driving output voltage                   | V <sub>OV2</sub> | V2  | V1 = 1.5 V                                                                                                                                                                                                        | 2.9  | 3.0   | 3.1       | V     | Products with                                                            |

| Reference output voltage for LCD driving | V <sub>OV1</sub> | V1  | I <sub>IN</sub> = 0 μA                                                                                                                                                                                            | 1.3  | 1.5   | 1.7       | V     | a booster only                                                           |

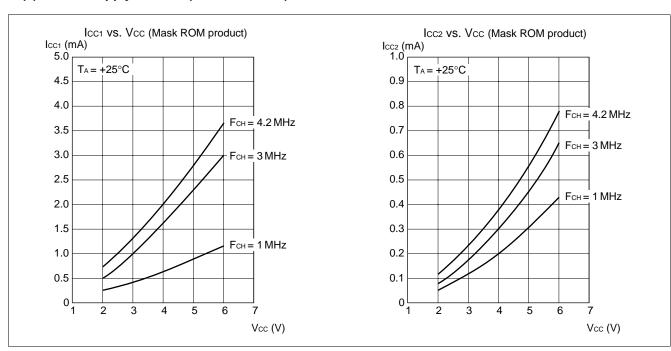

|                                          | Icc1             |     | FcH = 4.2 MHz,<br>Vcc = 5.0 V<br>$t_{inst}^{+3}$ = 0.95 $\mu$ s<br>Main clock                                                                                                                                     | _    | 3.0   | 4.5       | mA    | MB89151/A,<br>152/A, 153/A,<br>154/A, 155/A,<br>MB89PV150-<br>101 to 105 |

|                                          |                  |     | operation                                                                                                                                                                                                         | _    | 3.8   | 6.0       | mA    | MB89P155-101<br>to 105/201 to 205                                        |

|                                          | Icc2             |     | FcH = $4.2 \text{ MHz}$ ,<br>Vcc = $3.0 \text{ V}$<br>$t_{inst}$ = $15.2 \mu s$<br>Main clock<br>operation                                                                                                        | _    | 0.25  | 0.4       | mA    | MB89151/A,<br>152/A,153/A,<br>154/A, 155/A,<br>MB89PV150-<br>101 to 105  |

|                                          |                  |     |                                                                                                                                                                                                                   | _    | 0.85  | 1.4       | mA    | MB89P155-101<br>to 105/201 to 205                                        |

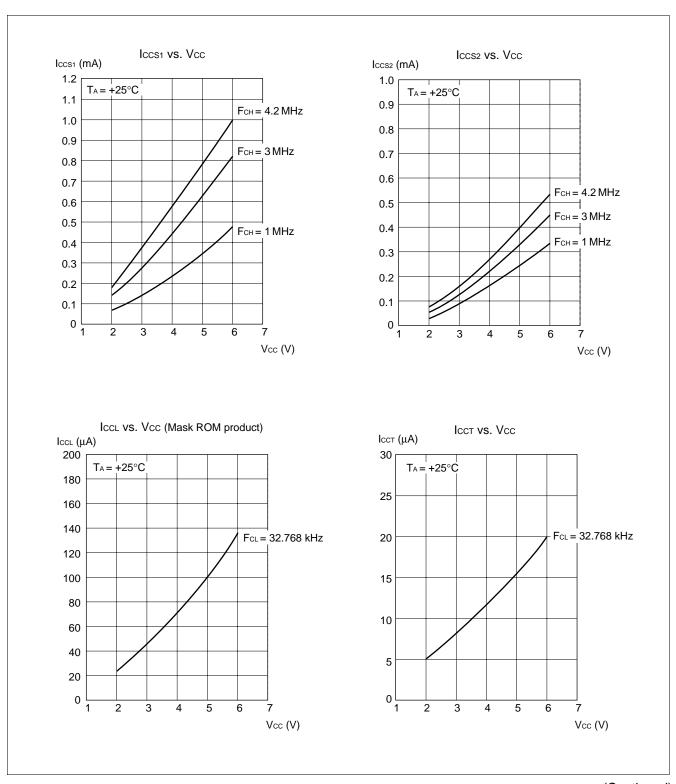

| Power supply current <sup>2</sup>        | ICCL             | Vcc | FcL = 32.768 kHz,<br>Vcc = 3.0 V<br>t <sub>inst</sub> <sup>-3</sup> = 61 μs<br>Subclock                                                                                                                           | _    | 0.05  | 0.1       | mA    | MB89151/A,<br>152/A, 153/A,<br>154/A, 155/A,<br>MB89PV150-<br>101 to 105 |

|                                          |                  |     | operation                                                                                                                                                                                                         | _    | 0.65  | 1.1       | mA    | MB89P155-101<br>to 105/201 to 205                                        |

|                                          | Iccs1            |     | $\begin{aligned} &\text{F}_{\text{CH}} = 4.2 \text{ MHz}, \\ &\text{V}_{\text{CC}} = 5.0 \text{ V} \\ &\text{t}_{\text{inst}}^{*3} = 0.95  \mu\text{s} \\ &\text{Main clock} \\ &\text{sleep mode} \end{aligned}$ | _    | 0.8   | 1.2       | mA    |                                                                          |

|                                          | Iccs2            |     | $F_{\text{CH}} = 4.2 \text{ MHz},$ $V_{\text{CC}} = 3.0 \text{ V}$ $t_{\text{inst}}^{*3} = 15.2  \mu\text{s}$ $Main \ clock$ $sleep \ mode$                                                                       | _    | 0.2   | 0.3       | mA    |                                                                          |

|                                          | IccsL            |     | $\begin{aligned} &\text{Fcl} = 32.768 \text{ kHz}, \\ &\text{Vcc} = 3.0 \text{ V} \\ &\text{t_{inst}}^{*3} = 61  \mu\text{s} \\ &\text{Subclock} \\ &\text{sleep mode} \end{aligned}$                             | _    | 25    | 50        | μА    |                                                                          |

(Continued)

$(Vcc = +5.0 \text{ V}, Vss = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                          | Symbol | Pin                 | Condition                                                                                                                     |      | Value |      | Unit  | Remarks                                                                |  |

|------------------------------------|--------|---------------------|-------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|------------------------------------------------------------------------|--|

| Parameter                          | Symbol | FIII                | Condition                                                                                                                     | Min. | Тур.  | Max. | Offic | Remarks                                                                |  |

|                                    | Ісст   |                     | Fc. = 32.768 kHz,<br>Vcc = 3.0 V<br>Watch mode                                                                                | _    | 10    | 15   | μΑ    | MB89151/2/3/4/5,<br>MB89P155-101<br>to 105,<br>MB89PV150-101<br>to 105 |  |

| Power supply current <sup>*2</sup> | Ісст2  | Vcc                 | Fal = 32.768 kHz,<br>Vcc = 3.0 V<br>• Watch mode<br>• During<br>reference<br>voltage<br>generator<br>and booster<br>operation | _    | 250   | 400  | μА    | MB89151A/2A/<br>3A/4A/5A,<br>MB89P155-201<br>to 205                    |  |

|                                    |        |                     |                                                                                                                               | _    | 0.1   | 1    | μΑ    | MB89151/2/3/4/5                                                        |  |

|                                    | Іссн   |                     | T <sub>A</sub> = +25°C,<br>Vcc = 5.0 V<br>Stop mode                                                                           | _    | 0.1   | 10   | μΑ    | MB89PV150-101<br>to 105,<br>MB89P155-101<br>to 105                     |  |

| Input capacitance                  | Cin    | Other than Vcc, Vss | f = 1 MHz                                                                                                                     | _    | 10    |      | pF    |                                                                        |  |

<sup>\*1:</sup> P31 and P32 are applicable only for products of the MB89150 series (without the "A" suffix). P40 to P47 and P50 to P57 are applicable when selected as ports.

In the case of the MB89PV150, the current consumed by the connected EPROM and ICE is not included.

Note: For pins which serves as the segment (SEG20 to SEG35) and ports (P40 to P47, P50 to P57), see the port parameter when these pins are used as ports and the segment parameter when they are used as segments. P31 and P32 are applicable only for products without a booster (applicable as external capacitor connection pins for products with a booster).

<sup>\*2:</sup> The power supply current is measured at the external clock, open output pins, and the external LCD dividing resistor (or external input for the reference voltage).

<sup>\*3:</sup> For information on tinst, see "(4) Instruction Cycle" in "4. AC Characteristics."

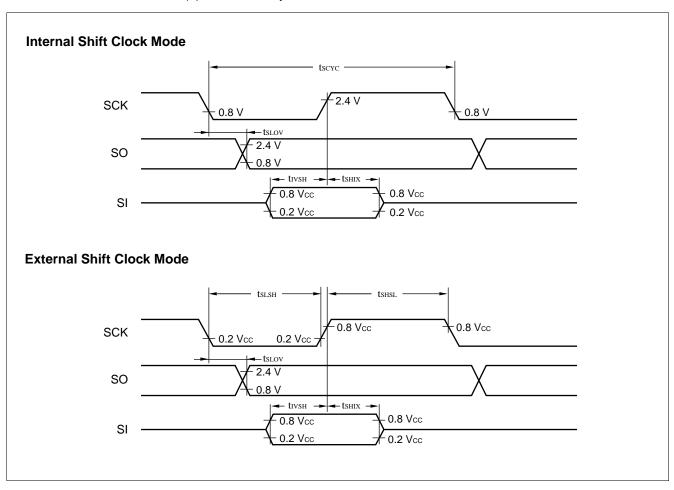

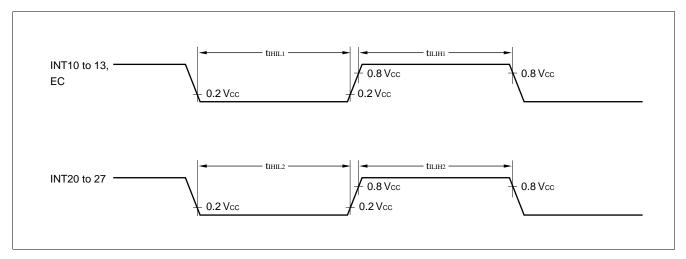

### 4. AC Characteristics

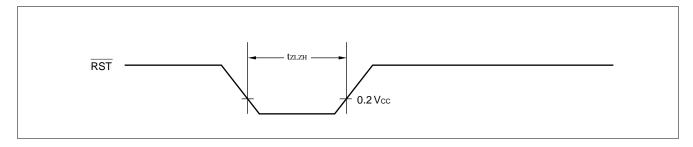

## (1) Reset Timing

$(Vss = 0.0 V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C)$

| Parameter           | Symbol             | Condition | Valu     | ne   | Unit  | Remarks |

|---------------------|--------------------|-----------|----------|------|-------|---------|

| Farameter           | Symbol Condition - |           | Min.     | Max. | Ollit | Remarks |

| RST "L" pulse width | <b>t</b> zlzh      | _         | 48 theyl | _    | ns    |         |

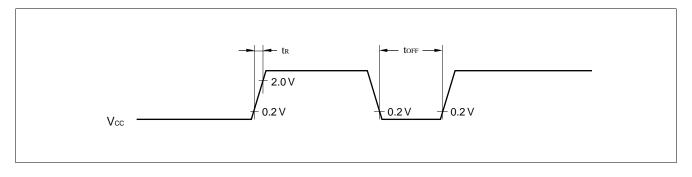

### (2) Power-on Reset

$(Vss = 0.0 V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C)$

| Parameter                 | Symbol   | Condition | Val  | lue  | Unit  | Remarks                      |  |

|---------------------------|----------|-----------|------|------|-------|------------------------------|--|

| rarameter                 | Syllibol | Condition | Min. | Max. | Oilit |                              |  |